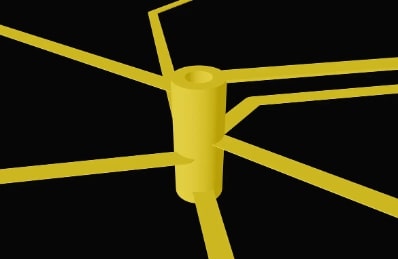

비아는 다층 PCB의 중요한 부분입니다. PCB 비아는 서로 다른 레이어의 구리 호일 라인을 연결하는 데 사용되는 전도성 채널입니다. 이는 일반적으로 이중층 보드 및 4층 보드와 같은 다층 구조이며 수십 개의 층에 도달할 수도 있습니다. 이들 층 사이에서 비아는 전도성 브리지 역할을 합니다. 회로 기판에 구멍을 뚫은 후 구멍 벽에 구리를 도금하여 형성된 전도성 채널입니다. 비아의 모양은 원형, 타원형 등이 될 수 있지만 가장 일반적인 것은 원형입니다.

PCB의 비아는 프로세스 측면에서 블라인드 비아, 매립 비아 및 관통 비아의 세 가지 범주로 나눌 수 있습니다.

막힌 구멍:

블라인드홀은 PCB의 표면층과 중간층만 연결하는 비아로 PCB 전체를 관통하지 않는다. 따라서 블라인드 비아는 다층 보드 설계, 특히 HDI(고밀도 상호 연결) 설계에서 공간을 절약하기 위해 매우 실용적입니다. 그러나 막힌 구멍의 드릴링 공정이 더 복잡하기 때문에 관통 구멍보다 비용이 더 높습니다.

다음을 통해 매장됨:

매립형 비아는 PCB의 각 레이어 내에 완전히 숨겨져 있으며 PCB의 내부 구리 레이어 2개 이상을 연결합니다. 상대적으로 공간 제약이 큰 고밀도 PCB에 이상적입니다.

관통 구멍:

스루홀은 PCB에서 가장 일반적인 유형의 스루홀입니다. PCB에 구멍을 뚫고 구리와 같은 전도성 물질로 채워서 생성됩니다.

비아는 종종 구성 요소를 PCB의 다른 레이어에 연결하고 구조적 지원을 제공하는 데 사용됩니다. 비아는 PCB의 상단 레이어에서 하단 레이어까지 드릴링됩니다. 베어 PCB가 태양을 향하게 하면 비아를 통해 햇빛이 통과할 수 있습니다.

PCB 스루홀 기능

신호 라우팅

다수의 PCB 보드는 신호 라우팅을 위해 스루홀을 사용합니다. 두꺼운 보드는 매립 비아 또는 블라인드 비아를 사용하고, 조명 보드는 마이크로 비아를 사용합니다.

전원 배선

블라인드 비아도 사용할 수 있지만 대부분의 PCB 보드에 있는 관통 구멍으로 인해 전원 및 접지 네트워크 라우팅을 위한 넓은 비아 사용이 제한됩니다.

탈출 배선

대형 표면 실장(SMT) 부품은 대부분 탈출 라우팅을 위해 관통 구멍을 사용합니다. 마이크로비아 또는 블라인드 비아는 이스케이프 라우팅에 가장 일반적으로 사용되지만, 비아-인-패드는 핀 수가 많은 BGA와 같은 견고한 패키지에 사용될 수 있습니다.

연결하다

관통 구멍이나 막힌 구멍을 사용하여 평평한 표면에 여러 연결을 제공할 수 있습니다. 예를 들어, 스티치된 비아가 있는 금속 스트립은 회로의 민감한 영역을 둘러싸고 이를 접지면에 연결하여 EMI 보호 기능을 제공합니다.

열전도

비아는 연결되는 구성 요소의 내부 평면 레이어에서 열을 전도하는 데 사용할 수 있습니다. 일반적으로 열 비아에는 밀집된 블라인드 비아 클러스터 또는 이러한 장치의 패드에 위치해야 하는 비아가 필요합니다.

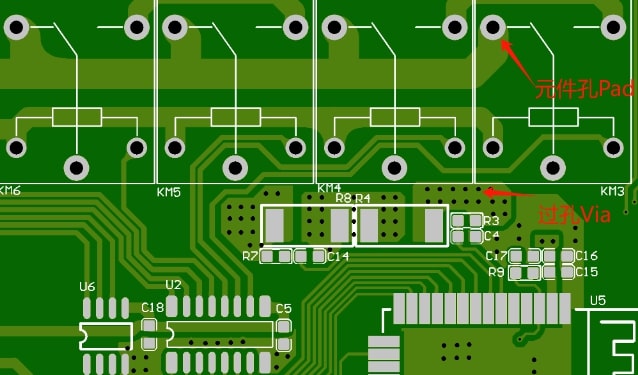

비아(Via)와 부품 홀(Pad)의 차이점은 무엇입니까?

PCB에서 Aperture는 비아홀(Via)과 부품홀(Pad)로 구분되어 있어 혼합되어서는 안됩니다.

비아는 일반적으로 양면을 전도하는 역할을 하며 가공 공정은 대개 오일로 덮는 것입니다. 부품 구멍(패드)은 일반적으로 플러그인 구멍으로 설계되며 플러그인 용접 중에 사용됩니다. PCB 비아(Via)와 부품 홀(Pad)이 혼합된 경우, 플러그인 패키지에서 비아(Via) 속성이 부품 홀로 잘못 사용되는 상황이 발생합니다. 비아홀 커버 오일을 선택하면 플러그인 홀이 잉크로 덮이거나 막혀 크기를 효과적으로 제어할 수 없습니다.

또 다른 상황은 부품 구멍(패드)이 관통 구멍으로 잘못 사용된 경우입니다. 그러면 소프트웨어가 자동으로 비아 창을 닫을 때 이를 효과적으로 인식할 수 없어 오일로 덮어야 하는 비아 구멍이 닫히게 됩니다. 기름으로 덮을 수 없습니다.

고속 PCB의 설계를 통해

고속 PCB 설계에서는 단순해 보이는 비아가 회로 설계에 큰 부정적인 영향을 미치는 경우가 많습니다. 비아의 기생 효과로 인한 부작용을 줄이려면 설계에서 다음을 수행하십시오.

(1) 합리적인 크기를 선택하십시오. 일반 밀도의 다층 PCB 설계의 경우 0.25mm/0.51mm/0.91mm(드릴링/패드/POWER 절연 영역) 비아를 사용하는 것이 더 좋으며 일부 고밀도 PCB의 경우 0.20mm/0.46mm도 사용할 수 있습니다. /0.86mm 비아의 경우 비스루 홀을 사용해 볼 수도 있습니다. 전원 또는 접지 비아의 경우 더 큰 크기를 사용하여 임피던스를 줄이는 것을 고려할 수 있습니다.

(2) PCB의 비아 밀도를 고려하면 POWER 절연 영역이 클수록 더 좋습니다. 일반적으로 D1=D2+0.41입니다.

(3) PCB의 신호 트레이스 레이어를 변경하지 마십시오. 즉, 비아를 최소화하십시오.

(4) 더 얇은 PCB를 사용하는 것은 비아 홀의 두 가지 기생 매개 변수를 줄이는 데 도움이 됩니다.

(5) 전원 및 접지 핀은 비아 홀과 핀 사이의 리드가 짧을수록 인덕턴스가 증가하므로 더 좋습니다. 동시에 전원 및 접지 리드는 임피던스를 줄이기 위해 최대한 두꺼워야 합니다.

(6) 신호에 대한 단거리 루프를 제공하기 위해 신호 레이어의 비아 근처에 일부 접지 비아를 배치합니다.

또한 비아 길이 역시 비아 인덕턴스에 영향을 미치는 주요 요인 중 하나입니다. 상단 및 하단 전도에 사용되는 비아의 경우 비아의 길이는 PCB 레이어 수의 증가로 인해 PCB 두께가 5mm를 초과하는 경우가 많습니다. 그러나 고속 PCB 설계에서는 Via Hole로 인한 문제를 줄이기 위해 Via Hole의 길이를 일반적으로 2.0mm 이내로 제어합니다. 길이가 2.0mm보다 큰 비아의 경우 비아 홀 직경을 늘려 비아 임피던스 연속성을 어느 정도 향상시킬 수 있습니다. 비아 길이가 1.0mm 이하인 경우 최적의 비아홀 직경은 0.20mm~0.30mm입니다.